VIDEO

Primer

#### Part 1 - Differential Signaling

| Introduction                                           | 1  |

|--------------------------------------------------------|----|

| Data Communication Technology Transformation           | 1  |

| Conventional Internal Data Bus Interface               | 1  |

| Conventional External Data Bus Interface               | 1  |

| Remote Data Communication Interface                    | 2  |

| Next Generation Data Bus Interface                     | 2  |

| Single-ended Signal Transmission                       |    |

| Differential Signal Transmission                       |    |

| Differential Signal Interconnects and Terminations     | 6  |

| Differential Interconnects                             |    |

| Differential Terminations                              | 8  |

| Physical Layer Standards for Serial Data Communication | 9  |

| InfiniBand                                             | 9  |

| Summary                                                | 14 |

#### **Part 2 - Differential Measurements**

| Introduction                                        | 14 |

|-----------------------------------------------------|----|

| Differential Measurement Fundamentals               | 14 |

| Differential Probe Specifications                   | 16 |

| P7350 Input Loading                                 |    |

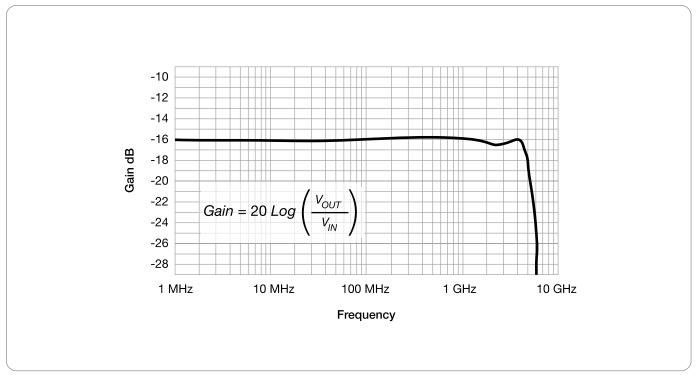

| P7350 Amplitude Response                            | 18 |

| P7350 Timing Response                               |    |

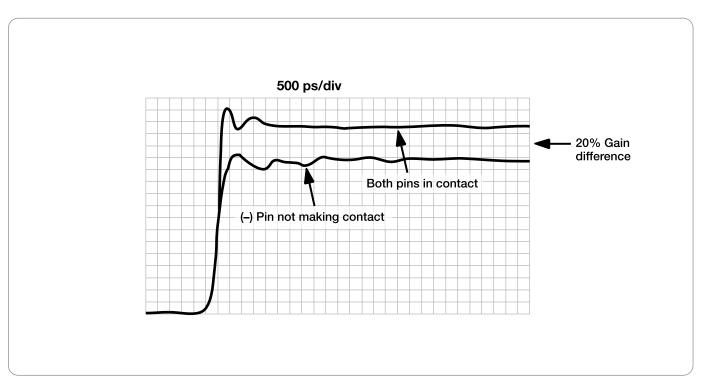

| Differential Probe Attachment Issues                | 22 |

| Differential Probe Attachment                       | 23 |

| Variable Spacing Adapter                            | 24 |

| Square Pin Adapter                                  | 24 |

| Solder-in Adapter                                   | 25 |

| Alternate Measurement Methods                       | 26 |

| Single-ended Measurements with a Differential Probe | 26 |

| Pseudo-differential Measurements                    | 27 |

| Measurement Channel Deskew                          | 28 |

| Differential SMA-input Probe                        |    |

| Summary                                             | 33 |

#### Part 1: Differential Signaling

#### Introduction

A significant transformation is taking place in data communication as digital interfaces are changing from wide bus structures to gigabit serial data links. Although there are a number of factors that are contributing to this change, the primary factor is the need to deal with increasingly difficult signal integrity issues as data rates continue to increase. Single-ended signaling with wide parallel buses appears to have finally reached its practical plateau in data rate and density. Differential signaling with gigabit serial data links is being selected as the technology for physical layer data transfer in many of the new data communication standards. The increased noise rejection and decreased noise generation, characteristic of differential signaling, have made possible this improved signal integrity performance. The application of differential signaling has also brought with it the need to understand differential measurement techniques. Tektronix is committed to providing the best differential measurement tools, including probing technology to make measurements in the most challenging applications. The first part of this two-part primer will examine the use of differential signaling in high-speed serial data links. The second part of the primer will review differential measurement techniques, with a special focus on the use of high bandwidth differential probes.

#### Data Communication Technology Transformation

The exponential growth in computing power, that has continued since the days of the first microprocessor, has driven a similar need for increased data communication transfer rate. For internal data communications between a computer and its memory or internal peripherals, a shared data bus has been the conventional interface structure. Internal communication data rates have been increased by increasing both the data clock rate and the width of the data bus. For external data communications between computers and local peripherals, a mix of high-speed parallel bus interfaces and lowspeed serial data interfaces have been used. Because of the need to limit the size of interconnect cables, the bus width of external parallel bus interfaces has remained relatively narrow; performance has been improved in external parallel bus interfaces primarily by increasing data transfer rate. For external data communications between computers and remote peripherals or in a local area network, the need to transfer data over longer distances has required serial data interfaces. For these remote data communication applications, as well, the trend has been towards dramatically increased data rates to support network processing and storage.

#### **Conventional Internal Data Bus Interface**

An example of a conventional internal data bus structure is the PCI interface. The PCI bus is the high-performance successor to the original IBM PC internal peripheral bus, the ISA bus. With a clock rate of 33 MHz and a 32-bit data path width, the PCI bus provided more than an order of magnitude improvement in data transfer rate over the ISA bus when it was introduced in the early 1990s. Even with a 133 MB/s data rate, the PCI bus has continued to evolve to try to keep up with the data transfer needs of more powerful processors. Updates to the PCI standard have doubled both the clock rate to 66 MHz and the data path width to 64 bits. A more recent extension to the PCI standard, called PCI-X, has extended the performance up to another order of magnitude with multi-rate clocking and a more efficient data transfer protocol. Multi-rate clocking is a data transfer enhancement technique for synchronous clocked systems where two (DDR) or four (QDR) data transfers occur in each clock cycle. As the data rate has increased, the PCI standards have been forced to limit the number of bus loads and bus length to reduce signal integrity problems. The load limit in the PCI-X standard, for example, is only one bus load, with bus expansion requiring buffered bridge techniques.

#### **Conventional External Data Bus Interface**

An example of an external data bus structure for local peripherals is the SCSI interface. SCSI is a high-speed, daisy-chained cable interface for interconnecting a variety of peripheral devices using an intelligent protocol for data transfers. The original SCSI implementation, defined in 1986, provided an 8-bit wide, bi-directional data bus with a data transfer rate of 5 MB/s. Up to eight peripheral devices could be chained together over a 20-foot maximum cable length with resistive terminations required at each end of the bus. Although an optional 16-bit wide data bus version, Wide SCSI, was defined in the first major enhancement to the SCSI standard, performance improvements to SCSI have been primarily through a repeated doubling of the bus data rate. Increases in the SCSI data transfer rate have been limited not only by the maximum signaling speed possible from signal transceivers, but also by interconnect physics. Because of signal dispersion caused by electrical cable losses, which become worse at higher data rates, there is a tradeoff between data rate, cable length, and the number of device loads for singleended SCSI signaling. Ultra SCSI, for example, provides for a 20 MHz data transfer rate, but reduces the maximum cable length to 10 feet for up to four device loads and only five feet for more than five device loads. The most recent enhancements to the SCSI interface have addressed these data rate and interconnect

Primer

limitations by introducing a low voltage differential (LVD) signaling specification. Because of the improved noise performance of differential signaling, SCSI LVD devices allow longer cable lengths to be used even in a bus interconnect environment.

#### **Remote Data Communication Interface**

An example of a remote data communication interface is Ethernet, which has been the dominant local area network standard since its introduction to industry in the early 1980s. Ethernet is a serial bus interface that initially provided a shared 10 Mb/s data rate between connected devices using a packet-based data transfer protocol. The initial version of Ethernet provided half duplex communication between devices connected together on a single shared transmission line. Ethernet handled the transmission contention problem between connected devices with a collision detection and retransmission protocol. Although the initial connection media used for Ethernet was coaxial cable, the use of less expensive twisted pair cable with phone jack connectors became dominant after the Ethernet 10Base-T standard was introduced in 1990. The first major improvement in Ethernet data transfer rate was a change from contention-based data transfers on a shared connection to switched data transfers on dedicated connections. Rapid increases in Ethernet data rates followed, first to 100 Mb/s with Fast Ethernet, then to 1000 Mb/s with Gigabit Ethernet (GBE), and most recently to 10 Gb/s with 10 Gigabit Ethernet (10GBE). At higher data rates Ethernet cabling distances are also limited by interconnect physics, but a variety of sophisticated physical layer implementations have been developed to overcome these limitations. An example is the multi-wire, multilevel logic technique defined for the 1000Base-T standard. The use of a sophisticated modulation technique, quality interconnect cable, and DSP processing has enabled the 1000Base-T standard to extend its maximum cable length to match the 100m distance limitation originally specified in the 10Base-T standard. At gigabit data rates the Ethernet physical layer implementation methods include optical interconnects as well as electrical interconnects. Although optical interconnects are more expensive than electrical interconnects, they have significantly better loss characteristics and will almost certainly become more common as data rates continue to increase.

#### **Next Generation Data Bus Interface**

In most of these data communication standard examples, the evolution towards faster and faster data rates was limited not only by current technology switching speeds, but also by signal integrity problems from using parallel busses and single-ended signaling. A practical limit appears to have been reached in the use of parallel, single-ended data transmission and a transformation is taking place to serial, differential data transmission. The parallel PCI bus, for example, may begin to be replaced within a few years by the highspeed serial bus called PCI Express. The PCI Express architecture uses low voltage, differential signaling, a packet-based data transmission protocol, and an extendable high-speed data rate beginning at 2.5 Gb/s. PCI Express uses a four-wire interface to provide a bi-directional transmit signal pair and receive signal pair on each serial data lane. It also defines the capability of aggregating lanes up to a width of 32 lanes, depending on the application. Although more wires are required per data bit than with a conventional data bus, the PCI Express message-based protocol and embedded clocking eliminates the need for the many data control signals required by a conventional data bus. The elimination of data transfer control signals in the PCI Express interface results in no major increase in the size of backplane connectors, even with four wires per bit for bi-directional differential signaling. The PCI Express data rate includes a 25% overhead for 8B/10B encoding. This data encoding provides a DC-balanced bit stream with high transition density and also provides special control characters for the data transfer protocol. The DC-balanced bit stream allows for ACcoupling and improved signal integrity, and the high transition density eases the task of clock recovery at the SERDES receiver.

(**NOTE:** A SERDES (serializer/deserializer) integrates the parallelto-serial and serial-to-parallel functions into a common building block component for high-speed serial transmission.) The common mode noise rejection of the differential signaling used by PCI Express also allows a low-voltage swing that reduces the power requirements of signal drivers and reduces EMI problems. The table below summarizes some of the differences between conventional and next-generation data transmission techniques:

#### Table 1. Comparison of High-speed Parallel and Serial Data Characteristics

|                         | Conventional<br>Transmission         | Next Generation<br>Transmission |

|-------------------------|--------------------------------------|---------------------------------|

| Signaling               | Single-ended                         | Differential                    |

| Data Width              | Parallel                             | Serial / Multi-lane             |

| Interconnect            | Shared Bus                           | Switched Point-to-Point         |

| Transmission            | Half Duplex                          | Dual Simplex                    |

| Clocking                | Synchronous                          | Embedded                        |

| Data Transfer           | Register-based                       | Message-Based                   |

| Data Element            | Byte/Word                            | Data Packet                     |

| Data Control            | Event Driven                         | Data Flow                       |

| Amplitude<br>Limitation | Reflections, Crosstalk,<br>and Noise | Loss and Dispersion             |

| Timing Limitation       | Skew                                 | Jitter                          |

One of the fundamental differences between conventional and nextgeneration data transmission is the type of signaling, which is changing from single-ended to differential. The next two sections of this primer will examine key differences between single-ended and differential signaling.

#### **Single-ended Signal Transmission**

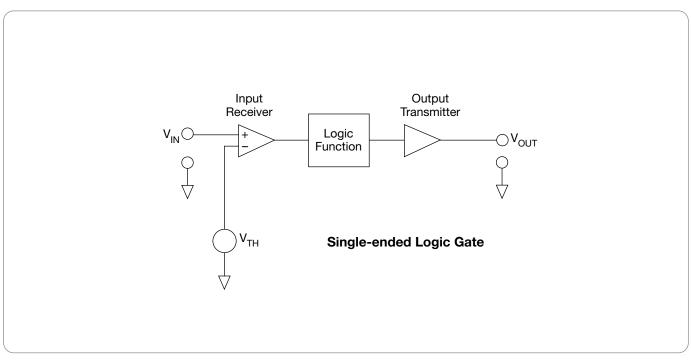

The transfer of digital signals through a physical logic circuit requires an output transmitter and an input receiver at each stage of the transfer process. This is true, in general, whether the communication takes place between logic gates within an ASIC or across a back plane in a high-speed serial data link. A simple logic inverter, for example, can be considered to contain a single input receiver, a single output transmitter, and an internal logic inversion function. For lower speed logic, the interface between logic gates is usually shown as a single wire connection and the data transfer process can be referred to as single-ended signaling. This single wire connection, however, is in reality an abstraction, since any physical electrical signal requires a return current path. The return current path for single-ended logic signals is usually considered to be "ground," which is a common reference for all the logic devices on a circuit board or system. Even for single-ended data signals switching at very high speeds, where the interconnect between devices must be considered a transmission line, the signal return current path is still usually ground, implemented as a solid ground plane on a circuit board layer.

The common ground connection for single-ended signals provides not only a return current path, but also a stable voltage reference. Ground is generally used as the stable voltage reference for the internal logic threshold generator of each logic gate input. As shown in the block diagram in Figure 1, all single-ended logic gate inputs are in reality voltage comparators. The input to the gate is compared against an internal logic threshold voltage to determine whether the received input signal is a logic HI or logic LO. The threshold voltage generator in Figure 1 is shown referenced to ground, although, depending on the device family, the threshold generator may actually be referenced to the logic gate power supply. For TTL logic the input logic threshold voltage is established by the turn-on characteristics of several bipolar transistors that are connected together to form the TTL circuit topology. In the case of ECL logic the input structure is a bipolar transistor differential pair whose emitters are coupled to a common current source. When used for single-ended logic, an internal voltage generator in the ECL logic gate drives one side of the differential pair. This provides a comparator threshold voltage for the ECL input signal, which is connected to the other side of the differential pair. The input logic threshold of CMOS logic is established simply by the turn-on characteristics of the interconnected p-channel and n-channel MOS transistors in the CMOS circuit topology.

Primer

#### Figure 1. Single-ended signaling.

Although single-ended logic families may generate their input logic threshold voltage in quite different ways, they all contain an embedded decision circuit. Even though single-ended logic gate inputs are shown schematically with only one input connection, there is actually an internal threshold comparison voltage that must be considered. The stability of this internal threshold voltage relative to the input signal swing can have a significant impact on the characteristics of the signal output from the logic gate. For example, noise sources that affect the input signal differently than the internal voltage threshold generator reference, can contribute to signal amplitude and timing distortion and even logic errors in the logic gate output. The switching of logic gate outputs, particularly devices with multiple outputs, can cause switching transients that effect the local ground potential, which then appears as noise injected into the internal threshold generator. Single-ended signals are susceptible not only to switching noise on the ground reference, but also to interconnection noise problems. As system clock rates have increased above 100 MHz and signal density has increased beyond 32-bit bus widths, signal integrity issues have become more of a problem in the interconnection of single-ended logic signals. Signal reflections due to transmission line effects, and crosstalk between signals due to interconnect interaction, have all become increasingly troublesome as signal data rates and signal density have increased. Increased data rates and signal density have also created more of a problem with EMI, which has increased the expense of system shielding. The point has finally been reached where many digital communication designs are migrating from single-ended to differential signaling because of the improved signal integrity and reduced noise possible with differential signaling.

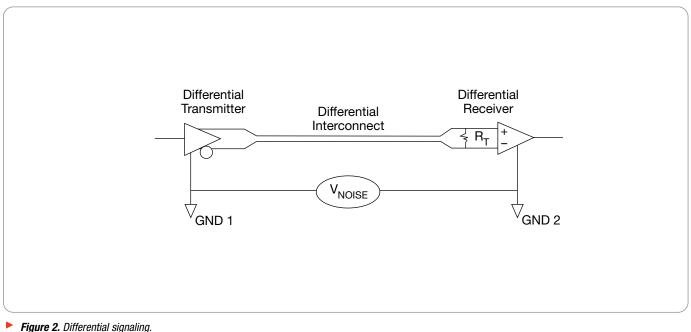

**Figure 2.** Differential signaling.

#### **Differential Signal Transmission**

A differential signal is transmitted on a dual signal path and the two signals are driven as a complementary pair, with one signal the logical inverse of the other. As shown in Figure 2, differential signaling includes a differential transmitter, a differential interconnect, and a differential receiver.

Differential signaling is not new, but has been used for many years in long haul transmission applications, where the transmitter and receiver ground potential may be significantly different. In Figure 2, this ground potential difference between the transmitter and receiver is modeled as a noise voltage source and can have both DC and AC components. An example of the historical use of differential signaling techniques in a low-speed, analog application is the common telephone service, where a balanced voice signal is transmitted on a twisted pair transmission line to a balanced phone receiver. Differential signaling is used in local telephone service because of its noise rejection performance. The recent use of differential signaling in high-speed data links has occurred because of similar noise rejection advantages. High-speed data links, however, use differential signaling at much higher frequencies where noise problems tend to be more severe, even for relatively short connections. The advantages of differential signaling in high-speed data transmission include the following:

- Common mode noise rejection

- Increased noise immunity

- Reduced crosstalk

- Reduced ground noise

- Reduced EMI

Differential signaling has much greater immunity to common mode noise problems than single-ended signaling because of both its interconnect topology and its signal processing technique. Differential signaling is able to reject common mode noise from ground potential variations between a transmitter and receiver, as well as crosstalk or other injected noise that is common to both signal paths. A differential signal interconnect is often routed as a coupled transmission line. This coupled transmission line topology provides a return current path between the coupled transmission lines, depending on the degree of coupling. For a balanced complementary signal transmitted on a tightly coupled transmission line, such as a twisted pair, the electric

Primer

fields are distributed primarily between the two signal conductors and the signal current propagating on one line returns on the other. The transmitted differential signal is then processed at the receiver as the voltage difference between the two lines. Differential signals thus carry along a built-in reference voltage that is largely independent of the ground potential at either the transmitter or the receiver. By processing the voltage difference between the two differential signals, the receiver effectively rejects most common mode noise that is present on both of the signals. By taking the difference between the two complementary signals, the differential receiver also produces twice the signal swing of a single-ended signal for improved noise immunity.

In addition to improved noise rejection, differential signaling also provides decreased noise generation, when compared to singleended signaling. Crosstalk noise has become a major problem in dense, high-speed single-ended designs because of increased field coupling between closely spaced single-ended transmission lines. Since the field distribution in a tightly coupled transmission line driven by a complementary signal tends to be primarily contained between the two conductors, differential signaling generates less crosstalk than single-ended signals. Crosstalk reduction can also be helped by the fact that the two lines in a coupled line pair can be routed closer together, which should generally allow greater separation between groups of coupled pairs. The balanced nature of differential signals also generally leads to a more constant switching current than is seen with single-ended circuits. The signal currents in differential drivers tend to be steered between the two outputs as the signal polarity switches, which results in a more constant load current compared to the load current spikes commonly seen with single-ended drivers. Reduced load current transients should also result in a reduction of that portion of ground noise that is caused by current spikes passing through the ground lead inductance. This is particularly true of single-ended drivers for wide parallel bus registers where many bits may switch state simultaneously. The improved noise immunity and high sensitivity of differential receivers also allows the use of reduced logic swings with differential signaling. This smaller signal swing and the balanced field distribution associated with differential signaling also generate less EMI.

Although there are many advantages in using differential signaling, which has led to its increased use in high-speed data applications, the following disadvantages should be recognized:

- Increased layout complexity

- The need for balanced signals and interconnect

Routing two traces for every signal, of course, results in more complexity than routing only one trace per signal. In addition, the common use of point-to-point connections rather than a shared bus structure results in separate paths for transmit and receive signals, effectively doubling the number of signal pairs required in a high-speed serial link. Since the two traces of a differential signal are generally routed together as a coupled pair, this also adds to the complexity of the routing task. The routing of the traces in a differential signal must also be matched carefully in length and provide a symmetrical interconnect path and matched termination. Imbalance in differential signaling paths leads to the generation of common mode currents and reduced common mode rejection at the receiver.

#### Differential Signal Interconnects and Terminations

At gigabit serial data rates, differential signal interconnects must be handled as controlled impedance connections. A high-speed differential interconnect, whether within a cable or routed across a circuit board, should be designed with a characteristic impedance that ideally matches the output impedance of the transmitter driver. In addition, as shown in Figure 2, the differential signal transmission line should be terminated with a resistance that also matches the characteristic impedance of the interconnect. Finally, the differential signal interconnect should be routed with as short and clean a connection as possible to minimize parasitics that can lead to signal integrity and jitter problems with gigabit signals.

#### **Differential Interconnects**

Several high-speed serial data standards define an electrical cable interconnect in order to provide an extended range communication link between computing and data storage nodes. This electrical cable interconnect definition includes both circuit board mount connectors as well as transmission cable specifications. Most pointto-point serial data standards define independent differential signaling paths in each direction, both a transmit signal and a receive signal. This is generally referred to as a dual simplex communication link. This results in the typical pinout for a single lane connector having a four-wire signal interface and usually multiple ground pads. An electrical cable for the transmission of high-speed serial data will often be shielded and the differential signaling path will typically be implemented with twisted pairs. Twisted pairs are used for differential signal impedance control and to minimize crosstalk between the transmit and receive signaling pairs. Twisted pairs are a good example of tightly coupled transmission lines, which tend to pass differential mode signals and suppress common mode signals. Some serial data standards define multiple physical signaling lanes in a single communication port. InfiniBand, for example, defines 1X, 4X, and 12X signal lane connectors and cables.

High-speed serial data interconnects on circuit boards also require the use of differential signal routing techniques. At gigabit data rates differential signal interconnects are often routed as coupled transmission lines. Because of the generally close spacing between circuit board traces and board ground planes, the degree of coupling between differential lines on a circuit board is much less than for twisted pairs, particularly for edge-coupled lines. This limited coupling between circuit board differential pairs means that it is not uncommon to see differential pairs routed separately on circuit boards as two uncoupled transmission lines. This is especially true where differential pairs must be routed through connectors or other tightly spaced barriers that force the differential signals to be separated for some distance anyway. Even if a differential pair is routed as two uncoupled traces, however, they must still be carefully controlled for matched delay and routed as symmetrically as possible. Since routing a differential pair as a closely spaced, coupled line makes it somewhat easier to observe symmetry in routing, the use of coupled line routing is still very commonly used. Closely spaced differential pairs are somewhat less susceptible to crosstalk from adjacent signals, although the limited coupling between circuit board differential pairs means that crosstalk may be an important issue. Crosstalk will always be worse, of course, in densely routed circuit boards.

Coupling between the traces of a differential pair also results in a decrease in the differential mode characteristic impedance, which must also be taken into account in the layout design. This decrease in the differential mode characteristic impedance is the result of a decrease in the effective inductance and an increase in the effective capacitance of a coupled transmission line when driven with complementary signals. For a differential mode signal, the effective inductance of coupled transmission lines decreases due to the mutual inductance of the lines and the effective capitance increases due to the mutual capacitance of the lines. As the differential mode characteristic impedance decreases due to coupling effects, the common mode characteristic impedance, resulting from identical signal drive to each trace, increases. For the normal complementary signal drive applied to a differential signaling pair, common mode characteristic impedance is usually not a significant issue, since its effects are seen only with differential signal path imbalance, which should be minimized.

Coupled lines can be routed in several different ways, depending on the layout requirements. Edge-coupled lines, where the traces are routed side-by-side on the same circuit board layer, are commonly placed on the outer layers as microstrip lines, although they can also be embedded as inner layer striplines. Broadside-coupled lines, where the traces are routed on top of each other on different circuit board layers, should generally be routed only on inner layers as striplines in order to provide a symmetrical structure.

Primer

At gigabit data rates there are a number of high frequency effects that need to be considered with differential signal interconnects. As signaling frequency increases, electrical signals suffer increased attenuation due to skin effect and dielectric losses. In the case of cable interconnects this attenuation is usually characterized as insertion loss and pulse dispersion. For circuit board interconnects these same frequency dependent loss effects are seen, although the dielectric loss tends to dominate at multi-gigabit data rates particularly for the commonly used FR-4 circuit board material. Because of these loss effects, the trace length of differential signals should be minimized for high-speed data signals. Several of the high-speed serial data standards allow the use of pre-emphasis or equalization to try to compensate for these frequency dependent loss effects. Pre-emphasis (sometimes also called de-emphasis) is an increase in the transmitter drive signal in the first bit period following a change in signal polarity; the transmitter drive is then reduced in bit periods where there is no signal polarity change. Equalization is a high pass filtering technique applied to the signal interconnect to try to compensate for the increase in interconnect attenuation with frequency. The simplest implementation of equalization is the use of an AC-coupling capacitor, which forms a high pass filter with the termination resistor. Since the termination resistor value is set by the characteristic impedance of the interconnect, the value of the AC-coupling capacitor should be selected to match the desired equalization response.

There are also parasitic elements present in the interconnect paths of most differential signals that become more of a problem as gigabit data rates continue to increase. One example is the use of vias in the signal routing path, which sometimes must be used to move a signal from one circuit board layer to another. A via in the signal path introduces a parasitic capacitance and inductance that generally acts as a discontinuity in the transmission line, leading to possible reflection problems and perhaps some slowing of the signal edge. A through-hole via may also introduce a short stub, if the signal is transferred between other than the outer layers. Blind or buried vias can be used to minimize via parasitics, but generally at an increased circuit board cost. If vias must be used in the signal routing path, via design should try to minimize parasitics and the parasitics should be matched in both traces of a differential pair. Electromagnetic modeling tools are now readily available for use in extracting via parasitics and other high frequency parasitic effects. Other examples of routing path parasitics are the parasitic input capacitance present at the input pin of a serial data receiver and the package parasitics present in a circuit board mounted serial data connector.

#### **Differential Terminations**

Properly matched source and load terminations can minimize the effect of interconnect parasitics by absorbing the reflections from parasitic discontinuities. Differential signal transmission lines should be terminated with a resistance that matches the characteristic impedance of the lines. Depending on the requirements of the differential driver and receiver circuits, this termination may be either a single resistor, which terminates only the differential mode impedance of the coupled line, or a multiple resistor network to terminate both the differential mode and common mode impedances of the differential pair. The more complex multiple resistor termination network may also include some common mode capacitance and the insertion of a DC bias. In the case of some serial data transceivers, these termination resistors are internal to the transceiver in order to minimize package parasitics and also to simplify the interconnection task. The termination resistor network is sometimes also affected by whether the differential signal path is AC or DC coupled, with AC coupling often used for DC-balanced protocols, like those with 8B/10B encoding.

Many of the new serial data communication standards implement the physical layer interconnect with SERDES devices or circuits. A SERDES provides the interface between a byte-wide data stream and a high-speed serial data stream and may contain encoding, synchronizing, and clock recovery circuitry. The high-speed serial output of some SERDES devices is implemented with current mode logic (CML). CML was originally a variant on a bipolar ECL output structure, where the output emitter followers were removed. CML can also be implemented, however, with MOSFET transistors, with the transistors configured as a steered current source switch. A CML output structure is a switched current source output topology that is usually loaded with an internal 50  $\Omega$  pull-up resistor on each line of the output pair. These CML output pull-up resistors serve as a source termination or back termination for the transmission line interconnect. The CML transmission line interconnect should, of course, also be terminated at the receiver end of the line. This use of both source and load terminations on the transmission line interconnect provides an ideal signal path for high-speed serial data signals and is being commonly used now, especially for multi-gigabit data signals.

#### Physical Layer Standards for Serial Data Communication

A number of high-speed serial data communication standards have been introduced recently to address the need for next generation I/O connectivity. Some examples of these new interface standards are

- InfiniBand

- PCI Express

- Serial ATA

- ► XAUI

Each of these standards shares a common 8B/10B encoding scheme and uses a similar differential signaling transmission topology, even though each was developed for a somewhat different application. InfiniBand was developed for use in the Internet data center to provide an improved data communication interface between compute servers, high-speed storage arrays, and Internet access devices. PCI Express was developed as a replacement for the PCI interface in high performance applications and was designed to be backward compatible with PCI at the software level. Serial ATA is a high-speed serial replacement for the parallel ATA interface (also called an IDE interface) used on many PC disk drives. XAUI is a 4-lane, chip-to-chip interface intended to provide a reliable connection between the system electronics and optical transceiver in a 10 Gigabit Ethernet interface.

Although each of these standards has some similar features, the underlying communication protocols and specification details differ significantly between the standards. Even the signaling rates are somewhat different, reflecting different applications and requirements. Although the signaling rate for InfiniBand and PCI Express is the same at 2.5 Gb/s, the signaling rate for Serial ATA is only 1.5 Gb/s, while the rate for XAUI is 3.125 Gb/s. In the case of XAUI, the use of 4 lanes each operating at 3.125 Gb/s results in the 12.5 Gb/s signaling rate required to give a 10 Gb/s data rate plus 25% overhead for 8B/10B encoding. The InfiniBand standard will now be examined in more detail, as an example of one of the new high-speed serial data communication standards.

#### InfiniBand

InfiniBand was developed as a next generation communication interface and is intended to be much more than just a local processor bus interface replacement. InfiniBand is designed for application flexibility over a variety of physical media. It is specified for use over short distances (<20 in.) as a processor backplane interface. It is also specified for use over extended distances (<17 m) as an electrical cable interface. It can even be used over longer distances as an optical cable interface, either with short wavelength fiber for distances of 75 m and more or with long wavelength fiber for a distance of up to 10 km. InfiniBand was designed to overcome the communication performance bottleneck in the Internet data center by addressing the limitations of a hierarchical, memory-mapped tree structure protocol like PCI. InfiniBand was designed as an intelligent I/O interface that would relieve compute servers, storage servers, and Internet routers of some of the processing overhead currently required to support I/O transfers.

Primer

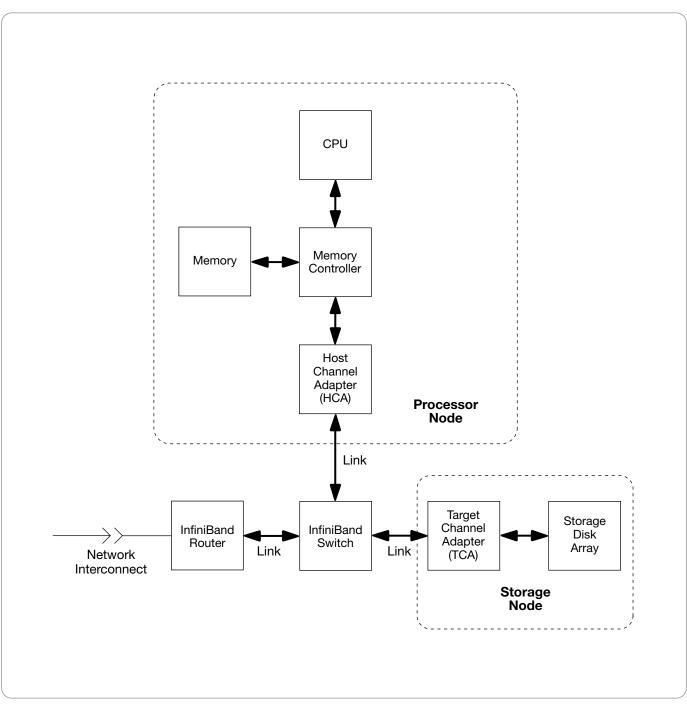

Figure 3. The InfiniBand architecture.

As shown in Figure 3, the InfiniBand architecture includes a

- Host Channel Adapter (HCA)

- ► Target Channel Adapter (TCA)

- InfiniBand Switch

- InfiniBand Router

The HCA is intended to reside in a compute server and manage its communication interface. The TCA is intended to reside in a storage

array and provide an intelligent interface to a physical disk drive. The InfiniBand Switch is a fully mapped switch interface between multiple HCAs and TCAs in a local communication network. The InfiniBand Router is designed as an interconnection between local networks using existing network protocols, such as IPv6. For high performance at the protocol level, the InfiniBand architecture provides peer-to-peer communication through device channels rather than hierarchical communication from a memory-mapped The InfiniBand Electrical Signaling specifications are defined in detail in Chapter 6 of Volume 2 of the InfiniBand Architecture specification. Table 2 highlights the key electrical specifications, which will be examined in more detail in the section that follows.

#### Table 2. InfiniBand Electrical Signaling Specifications (partial list from Release 1.1)

| Impedance | 9                    |                               |      |      |       |

|-----------|----------------------|-------------------------------|------|------|-------|

| Driver    | Symbol               | Parameter                     | Max  | Min  | Units |

|           | Z <sub>D</sub>       | Differential Output Impedance | 125  | 75   | Ω     |

|           | Z <sub>SE</sub>      | Single Ended Output Impedance | 75   | 30   | Ω     |

|           | Z <sub>MSE</sub>     | Single Ended Impedance Match  | 10   |      | %     |

| Receiver  |                      |                               |      |      |       |

|           | Z <sub>RTerm</sub>   | Termination                   | 62.5 | 40   | Ω     |

|           | L <sub>DR</sub>      | Differential Return Loss      |      | 10   | dB    |

|           | L <sub>CMR</sub>     | Common Mode Return Loss       |      | 6    | dB    |

| Amplitude |                      |                               |      |      |       |

| Driver    | Symbol               | Parameter                     | Max  | Min  | Units |

|           | V <sub>diff</sub>    | Differential Output (pp)      | 1.6  | 1.0  | ۷     |

|           | V <sub>CM</sub>      | Common Mode Voltage           | 1.0  | 0.5  | V     |

|           | V <sub>disable</sub> | Disabled Mode Output          | 1.6  | 1.0  | V     |

| Receiver  |                      |                               |      |      |       |

|           | V <sub>RSense</sub>  | Input Sensitivity (pp)        |      | 175  | mV    |

|           | V <sub>RCM</sub>     | Common Mode Voltage           | 1.25 | 0.25 | V     |

|           | V <sub>tt</sub>      | Termination Voltage           | 1.0  | 0.5  | ۷     |

| Timing    |                      |                               |      |      |       |

| Driver    | Symbol               | Parameter                     | Max  | Min  | Units |

|           | UI                   | Unit Interval                 | 400  | 400  | ps    |

|           | t <sub>DRF</sub>     | Driver Rise/Fall Time         |      | 100  | ps    |

|           | J <sub>T1</sub>      | Total Jitter at Driver        | .35  |      | UI    |

| Receiver  |                      |                               |      |      |       |

|           | t <sub>REye</sub>    | Eye Opening                   |      | 140  | ps    |

|           | J <sub>TR</sub>      | Total Jitter at Receiver      | .65  |      | UI    |

|           | S <sub>RBtB</sub>    | Total Skew                    | 24   |      | ns    |

central control processor. InfiniBand data transfer protocols support prioritization of data packets that, at the high InfiniBand transfer rate, enables the transfer of real time data with guaranteed quality of service. The InfiniBand protocols also support more reliable data communication through the use of error checking codes embedded in InfiniBand data packets.

At the physical layer, InfiniBand provides improved performance through its point-to-point, serial data interface. An InfiniBand communication lane includes two independent differential signaling paths, one for transmit and one for receive, both operating at a 2.5 Gb/s rate. The InfiniBand standard also includes scalable performance through the use of multiple lane links, with 1X, 4X, and 12X links currently specified. As a server backplane interface, the InfiniBand interface is hot-pluggable, which allows for ease of use in scaling compute power in servers and is beneficial for maintenance of a reliable server system. As a cabled interconnect interface between compute servers or storage arrays, the InfiniBand interface has been optimized for low-power operation by limiting the electrical cable length to 17 m, sufficient for the intended application in an Internet data center.

The InfiniBand impedance specifications define the limits for the InfiniBand signal interconnect environment. Since the InfiniBand differential signaling interconnect is designed for a nominal 100  $\Omega$  differential impedance, it might seem unusual for the driver impedance parameters,  $Z_D$ ,  $Z_{SE}$ , and  $Z_{RTerm}$  to have such loose tolerances. Although the loose impedance tolerance specified will result in poorer

▶ Primer

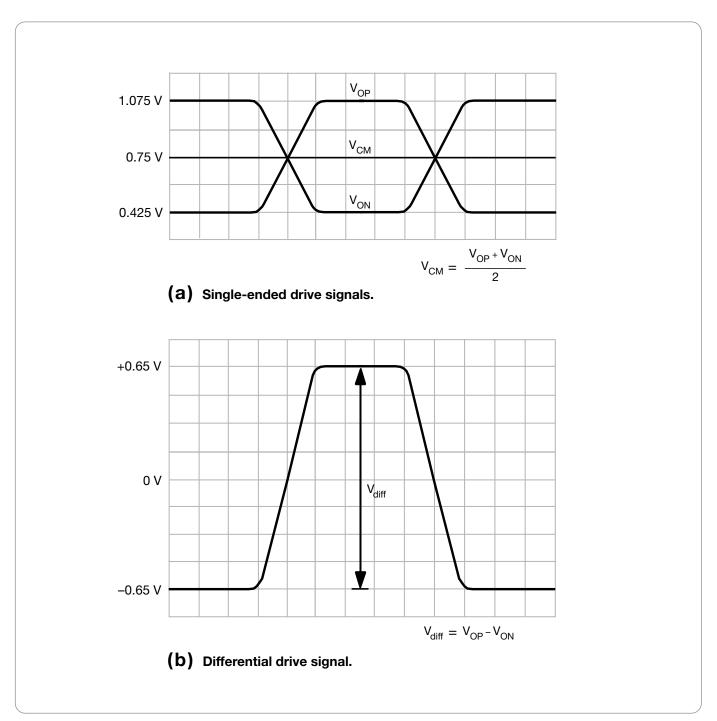

Figure 4. InfiniBand driver signals: V<sub>CM</sub> = 0.75 V; V<sub>diff</sub> = 1.3 V.

signal integrity under worst-case conditions, it provides compatibility with integrated circuit processes. The use of integrated driver source resistance and receiver termination resistance, in turn, will actually help signal integrity because of the reduced termination parasitics. The single-ended impedance matching parameter,  $Z_{\rm MSE}$ , is also compatible with integrated circuit processes and such matching is

necessary to minimize differential signal imbalance. Differential signal imbalance causes some of the differential mode signal to be converted to a common mode signal, which can result in possible signal integrity or EMI problems. The receiver termination parameter,  $Z_{RTerm}$ , is a single-ended impedance value and the differential termination impedance is of course double that value.

The receiver return loss parameters,  $L_{DR}$  and  $L_{CMR}$ , are intended to guarantee a clean transmission line environment into the receiver. Differential and common mode return loss measurements, however, require a network analyzer with a mixed mode S-parameter test set and mixed mode conversion software. Most of the impedance parameters are specified over a bandwidth of 100 MHz to 1.875 GHz, a frequency range that includes most of the signal power spectrum for an 8B/10B encoded InfiniBand signal at 2.5 Gb/s.

The InfiniBand amplitude specifications define the allowable range of signal voltage between the driver and receiver. Since InfiniBand uses differential signaling, both differential mode and common mode parameters are specified. The common mode parameters are significant only for DC-coupled interconnections. The InfiniBand standard requires that cable connections be AC-coupled and allows backplane connections to be optionally AC-coupled. The standard also suggests a minimum DC blocking capacitance of 4700 pF, which gives a coupling impedance of much less than 1  $\Omega$  at 250 MHz. The 250 MHz frequency is noted here, since it is the lowest signaling frequency for an 8B/10B encoded signal with a 2.5 Gb/s signaling rate. This is the result of the 5-bit run length limit that is characteristic of 8B/10B encoding. The driver differential output parameter is specified for backplane interconnects at the output pins of the driver and will be attenuated due to interconnect losses if measured further down the interconnect path. If a backplane driver uses preemphasis, the differential output parameter range applies only to the first bit period following a transition and may be lower for later bits after the pre-emphasis drive is removed. For cable interconnects the differential output parameter is specified at the cable port and its range is valid with or without pre-emphasis. As shown in the Figure 4 example, the differential output parameter is specified as a peak-to-peak voltage difference, thus the signal swing on each pin of the driver is half that value. It should be noted that the V parameter signal shown in Figure 4(b) can only be measured with a differential probe connected between the two signals in Figure 4(a), or by calculating the waveform difference of the two signals in Figure 4(a), measured with single-ended probes. The signal shown in Figure 4(b) thus represents the result of the receiver processing of the two complementary input signals from the driver shown in Figure 4(a) and cannot be measured directly as a singleended signal. When the transmitter driver is in a disabled mode

state, the differential output voltage is allowed to drop to zero volts, although the driver pins should still be held within the common mode voltage range. When the transmitter is in disabled mode and no differential voltage is applied to the receiver, the receiver must also be disabled to guarantee no false signals are generated. The input sensitivity parameter of an InfiniBand receiver is the minimum peak-to-peak differential signal that will be properly detected with the specified maximum bit error rate of  $1 \times 10^{-12}$ . Detection of signals below the input sensitivity level is not guaranteed. The receiver termination voltage range and common mode voltage range are only applicable for DC-coupled interconnects to the driver.

The InfiniBand timing specifications are designed to guarantee that the critical jitter characteristics of a high-speed serial link are controlled for reliable link performance. The InfiniBand timing parameters are based on eye pattern measurements\*1. A unit interval (UI) of an eye pattern is the time window of a single bit period, which for 2.5 Gb/s signaling is 400 ps. The jitter on a signal can be observed at the transition edges on an eye pattern. The total jitter at the driver, which includes both random and deterministic litter components. is specified for an InfiniBand backplane interconnect at a little over one-third of a UI. The total jitter spec for a cabled interconnect, although not included in the partial specification table, is more restrictive than for a backplane interconnect to allow more margin for jitter accumulation in a long cable interconnect. The difference between the total jitter allowed at the transmitter and the larger total jitter allowed at the receiver is an indication of the jitter that is allowed to accumulate over the length of the interconnect. The receiver eye opening parameter is a measure of the jitter-free time period in the center of the eve pattern at the receiver, and when combined with the receiver input sensitivity parameter can be used to define an eye pattern mask for signal transmission within allowable error limits. There are now more sophisticated jitter analysis tools, such as TDSJIT3 or TDSRT-Eye<sup>™</sup> to use with real-time Tektronix oscilloscopes. These tools enable a more detailed analysis of the different jitter components.

<sup>\*1</sup> An eye pattern is an overlapped display of signals showing the accumulation of all signal states in a single bit period window. It is called an eye pattern because of its eye shaped display and because the characteristic closing of the eye pattern as attenuation and jitter increase with interconnect length, causing the signal to no longer be "visible" to the receiver. Eye pattern jitter parameters are specified in terms of a unit interval.

The driver rise and fall time parameters are specified as minimum values to control signal integrity problems that become worse with faster edge speeds. The driver maximum rise/fall time, although not directly specified, is effectively controlled by the receiver eve opening mask, since too slow a transition at the transmitter will continue to slow through the interconnect and will cause mask violations at the receiver. It should be noted that the driver rise/fall time is specified as a 20-80% measurement, rather than the 10-90% measurement commonly used to specify the performance of measurement instruments. Since rise/fall times occur at signal transitions, if pre-emphasis is used in a driver, the rise/fall time measurement is made on the signal with pre-emphasis applied. The total skew parameter at the receiver may seem to be extremely large, since it equals 6 UI, but it represents skew across physical lanes of an InfiniBand port and can be compensated as part of the data synchronization and alignment process in the InfiniBand training protocol. The skew allowed between lanes driven from a single transmitter driver is much less (500 ps) and the skew between lines of a single lane differential pair, although not directly specified, should be kept as small as possible to ensure transmitting a good signal and to reduce signal integrity and EMI problems.

#### Part 1 Summary

This brief review of key critical signal parameters that must be measured to guarantee compliance with the InfiniBand physical layer standard is typical of the measurement requirements for new high-speed serial data communication standards. The standard tool used to make most of the voltage and timing measurements discussed in the last section is a high performance oscilloscope. Although at one time the high bandwidth necessary to measure gigabit data signals required the use of sampling oscilloscopes, dramatic improvements in real time oscilloscope performance have now made the use of real time oscilloscopes common in serial data measurements. Although an oscilloscope is a common measurement tool for testing standards compliance and debugging electronic circuitry, its use in making differential signaling measurements is perhaps less familiar. The focus of Part 2 of this primer will be on differential measurements, with an emphasis on their application to high-speed serial data communication signals.

#### **Part 2: Differential Measurements**

#### Introduction

Part 1 of this primer discussed how the transformation led from single-ended signaling to differential signaling in new interface standards. It reviewed key differences between single-ended and differential signaling and the advantages of using differential signaling in high-speed data links. The application of differential signaling has also brought with it the need to understand differential measurement techniques. Because two single-ended signals are combined to make one differential signal, differential signaling adds complexity to signal characterization. Differential signaling generally requires that both differential mode and common mode parameters be specified. Similarly, differential measurements must deal with measuring both the differential mode and common mode parameters that describe the differential signaling interface. Part 2 of this primer will review differential measurements and the tools used to measure differential signals. Because of their importance in measurement fidelity, high-performance differential probes will be examined in considerable detail.

#### **Differential Measurement Fundamentals**

Although single-ended measurement tools can be used to indirectly measure differential signals, the use of differential measurement tools allows a designer to see the differential signal in much the way a differential receiver sees it. A good differential measurement tool must have the following characteristics to be able to measure a high-speed differential signal with good signal fidelity:

- High frequency response

- ► High common mode rejection

- High sensitivity and response accuracy

- Low noise floor

- Light circuit loading (unless designed to be a broadband termination)

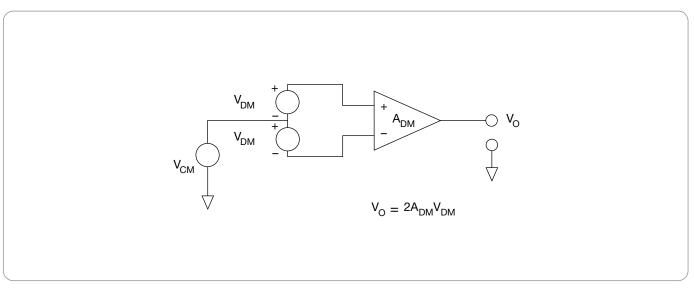

An idealized differential amplifier is shown in Figure 5 driven by a combination of differential and common mode voltage sources. The voltage sources in Figure 5 are configured to model a complementary differential signal. The differential amplifier in Figure 5 might be considered to represent an ideal differential probe model, with infinite input impedance, a fixed differential mode gain, infinite CMRR, and an ideal 50  $\Omega$  output impedance to drive a probe cable.

An ideal differential amplifier amplifies the voltage difference between its inputs, totally rejecting any voltage common to both inputs. Referring to Figure 5, the voltage, V+, on the differential amplifier positive input is

$$V_{+} = V_{CM} + V_{DM}$$

The voltage, V–, on the differential amplifier negative input is

$$V_{-} = V_{CM} - V_{DM}$$

The resulting difference voltage output from the differential amplifier with fixed differential mode gain,  $A_{_{\rm DM}}$ , is

$$V_{o} = A_{DM} * (V_{+} - V_{-})$$

$$V_{o} = A_{DM} * [(V_{CM} + V_{DM}) - (V_{CM} - V_{DM})]$$

$$V_{o} = A_{DM} * (2 V_{DM})$$

This resulting output voltage shows the rejection of the common mode input voltage and the doubling of the single-ended, differential mode input voltage.

The previous differential input equations show that the common mode voltage represents the average of the voltage on the two differential inputs

$$V_{\rm CM} = (V_{+} + V_{-}) / 2$$

Similarly, the differential voltage output from a unity gain differential amplifier is simply the voltage difference between the two differential inputs

$V_{\text{DIFF}} = V_{+} - V_{-}$

A non-ideal differential amplifier will have slight imbalances between its two inputs, which results in a small portion of the common mode input voltage being passed through to the output. This common mode voltage signal in the output can be considered to be an undesirable error term, since part of it may result from ground noise or other common mode noise sources. Since it is possible to measure the response of a non-ideal differential amplifier to a purely common mode input signal, the common mode gain for the amplifier can be calculated:

$$A_{CM} = V_0 / V_{CM}$$

with  $V_{DM} = 0$

A measure of the performance of a differential amplifier in rejecting the undesirable common mode input signal is called the common mode rejection ratio (CMRR)

#### CMRR = A<sub>DM</sub> / A<sub>CM</sub>

Since the CMRR of a quality differential amplifier is a very large value, it is often expressed in decibels

#### CMRR = 20 log ( $A_{DM} / A_{CM}$ ) in dB

As an example of the magnitude of the common mode error term in a good quality differential amplifier, consider an amplifier with a DC CMRR of 60 dB and a 1 V DC common mode input signal. Since a 60 dB CMRR is a 1000:1 gain ratio, the resulting DC error from the 1 V common mode input is 1 mV. The polarity of the 1 mV error term is unknown, since the CMRR measurement contains no phase information. Since common mode signals will, in general, have both AC and DC components, the CMRR frequency response of the differential amplifier must be considered. The CMRR of a typical Primer

differential amplifier is generally highest at DC and drops off with increasing frequency, becoming significantly worse at high frequencies. This decrease in CMRR with frequency is a measure of the difficulty in maintaining balanced amplifier response as high frequency parasitic effects increase.

#### **Differential Probe Specifications**

An oscilloscope specifies its measurement performance at its front panel input connector. The purpose of an oscilloscope probe is to extend specified measurement performance from an oscilloscope front panel to the circuit-under-test with the highest possible signal fidelity. Making high-fidelity measurements with a probe a meter or two away from an oscilloscope requires that the probe be connected to the oscilloscope with a high frequency, shielded cable. Since the coaxial cables commonly used to make this connection have a characteristic impedance of 50  $\Omega$  and a distributed capacitive load of about 30 pF/ft., a probe design must compensate for this cable loading. Passive probes, which connect to a high impedance, 1 M $\Omega$ oscilloscope input, compensate for cable loading by using a high impedance probe tip attenuator. The high impedance 10X attenuator commonly used in passive probes generally limits probe bandwidth to 500 MHz or less. For higher frequency applications, active probes are generally used.

Although an ideal differential probe would be able to measure a signal with perfect fidelity and without any loading of the signal, any real probe has limitations that must be understood. By understanding the limitations of practical probe performance, a user can more readily relate measured signal response to real signal response. By choosing a probe and scope whose performance is adequate for the measurement application and using the probe in a manner which minimizes its limitations, a user will get the best match between measured and real signal performance. The limitations of probe response are quantified with the probe performance specifications. Table 3 lists some of the key performance specifications for the Tektronix P7350, which is a high performance differential probe designed for use in applications like high-speed serial data signal analysis. The definition of the P7350 specifications listed in Table 3 will be examined in some detail in the following section. It should be noted that Table 3 contains a mix of guaranteed and typical specifications. The P7350 probe data sheet or User Manual should be consulted for more detail about a specific parameter.

## Table 3. P7350 ElectricalCharacteristics

| Parameter                              | Specification     | Notes                                      |  |

|----------------------------------------|-------------------|--------------------------------------------|--|

| Input Loading                          |                   |                                            |  |

| Differential Mode<br>Input Resistance  | 100 kΩ ±2%        |                                            |  |

| Common Mode Input<br>Resistance        | 50 kΩ ±2%         | per side                                   |  |

| Differential Mode<br>Input Capacitance | <0.3 pF           | at 100 MHz                                 |  |

| Common Mode Input<br>Capacitance       | <0.45 pF          | per side at 100 MHz                        |  |

| Amplitude Response                     |                   |                                            |  |

| DC Gain Accuracy                       | 0.16 ±2%          | 6.25x attenuation                          |  |

| Differential Mode<br>Input Range       | ±2.5 V            | differential offset = 0                    |  |

| Common Mode<br>Input Range             | +6.25 V to -5.0 V |                                            |  |

| Maximum Input<br>(non-destructive)     | ±15 V             |                                            |  |

| Differential Offset<br>Range           | ±1.25 V           |                                            |  |

| CMRR                                   | DC<br>1 MHz       | >60 dB<br>>55 dB                           |  |

|                                        | 30 MHz            | >50 dB                                     |  |

|                                        | 1 GHz             | >30 dB                                     |  |

| Timing Response                        |                   |                                            |  |

| Bandwidth                              | DC to 5 GHz       | 3 dB bandwidth                             |  |

| Rise Time                              | <100 ps<br><65 ps | 10 to 90% rise time<br>20 to 80% rise time |  |

Active probes, which are designed to connect to a broadband, 50  $\Omega$ oscilloscope input, compensate for cable loading by using a high frequency buffer amplifier in the probe tip. The buffer amplifier in an active probe tip has a 50  $\Omega$  output driver stage that drives the distributed probe cable loading as a transmission line. Driving the probe cable as a transmission line provides broadband frequency response. The probe cable, however, like all transmission lines is susceptible to electrical cable loss. To guarantee signal fidelity, the probe buffer amplifier must compensate for probe cable frequency dependent loss effects, up to the frequency limit of the probe. The use of a high-frequency buffer amplifier in the probe head also reduces probe loading effects at the probe tip. The addition of a high impedance attenuator in front of the buffer amplifier reduces the effect of the buffer amplifier input capacitance and increases input dynamic range. These input attenuator advantages, however, are traded off against reduced signal-to-noise ratio.

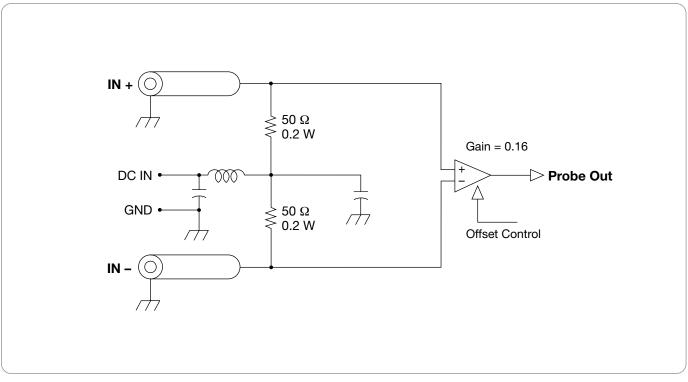

#### Figure 6. First-order differential probe load model for the P7350.

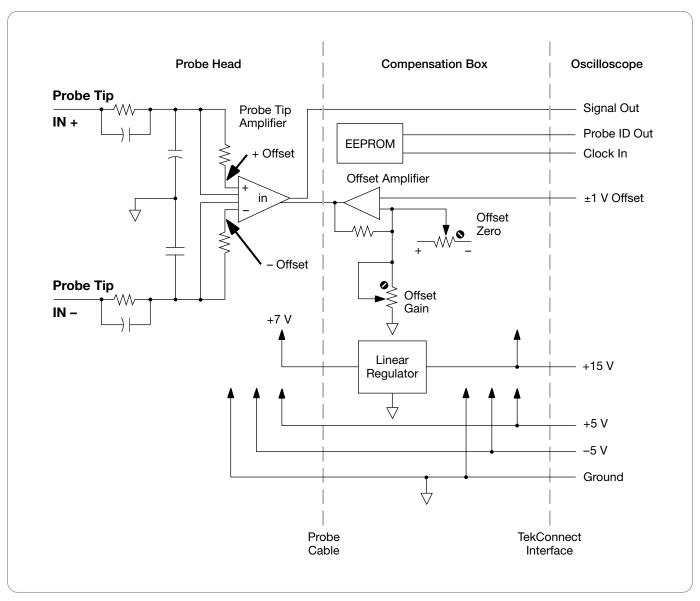

In the case of a differential probe, the probe provides a differential measurement capability at the probe tip and connects to a single oscilloscope channel input. The P7350 is a high bandwidth, differential probe with an active hybrid circuit in the probe head. The P7350 active hybrid contains a high impedance, laser-trimmed attenuator and differential buffer amplifier. By placing the buffer amplifier in the probe head, very close to the probe input pins, probe loading effects are minimized and CMRR can be maximized. The probe head is miniaturized to allow its use in physically restrictive environments and to minimize parasitics in the probe head circuitry is powered and controlled by a TekConnect<sup>™</sup> interface, the standard probe interface on all Tektronix high-performance oscilloscopes.

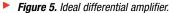

#### P7350 Input Loading

An ideal differential probe could be attached to a differential circuit and make measurements without disturbing the circuit under test. Any real probe, however, has a finite load impedance that may need to be accounted for in measurements, particularly at high frequencies. A first-order load model for the P7350 differential probe is shown in Figure 6. As expected, the probe load model shows a balanced structure, which to first order is identical for each of the two inputs. The input resistor, R<sub>I</sub>, is a damping resistor with a typical value for a P7350 probe of about 130  $\Omega$ . The common mode input capacitance, C<sub>s</sub>, is one-half the capacitance that would be measured with the inputs shorted together, and for the P7350 probe has a typical value of about 0.4 pF. The differential mode input capacitance is the capacitance measured differentially between the two inputs, and is the sum of C<sub>D</sub> and the series combination of the two common mode input capacitors. For the P7350 probe, which has a typical value for C<sub>D</sub> of about 0.1 pF, this results in a differential mode input capacitance of about 0.3 pF. The common mode input resistance, R<sub>s</sub>, for the P7350 differential probe is 50 k $\Omega$ , which results in a differential mode input resistance, R<sub>DM</sub> of 100 k $\Omega$ .

This first-order probe load model provides useful information on probe loading at lower frequencies. From DC up to about 1 MHz the probe differential mode input impedance is primarily resistive, and for the P7350 probe is constant at 100 k $\Omega$ . Above about 1 MHz the probe differential mode input capacitance begins to reduce the probe input impedance until it reaches the P7350 damping resistance of 130  $\Omega$  for frequencies above 1 GHz. Although this discrete component model does provide some useful information at lower frequencies, it should be noted that the model doesn't include any probe input inductance. Neither intrinsic inductance in the probe hybrid nor attachment inductance from the probe pins or connection adapters is included in the first-order model. Probe input inductance will add resonant effects to this first order probe load

Primer

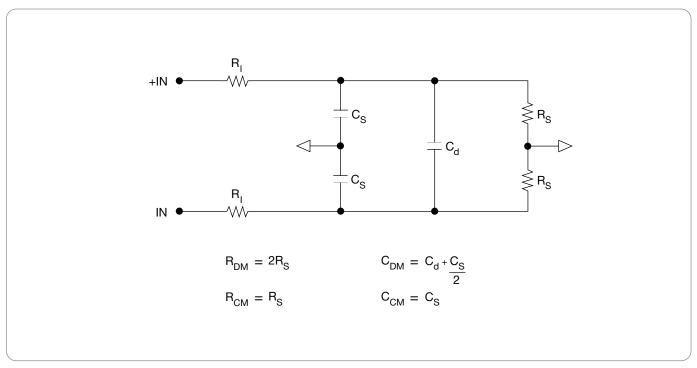

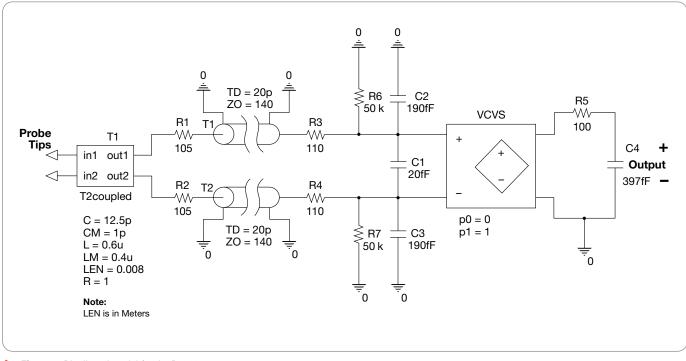

Figure 7. Distributed model for the P7330.

model. The addition of probe interconnect adapters, which generally add more inductance to the relatively small probe pin inductance, increases probe resonant overshoot and may require additional damping resistance at the measurement node. Tektronix does provide more accurate distributed component models on its web site for most of its high performance probes, including differential probes. The distributed component model for the P7330 probe, for example, is shown in Figure 7. The P7330 probe is quite similar to the P7350 probe, but has a bandwidth specification of only 3.5 GHz. The P7330 distributed model contains a coupled transmission line input and a simplified amplifier output model with a one-pole roll-off response. This distributed component model provides accurate modeling of probe loading effects up to the limit of the probe frequency response. Although optimized for probe loading effects, the distributed component model also provides first-order transient and frequency response performance for the probe.

#### **P7350 Amplitude Response**

In order to measure an electrical signal with high fidelity, the gain of a probe amplifier must be carefully controlled over a wide frequency range. The gain of an ideal probe amplifier would be constant from DC out to frequencies near its specified bandwidth limit and then drop off fairly rapidly. The gain roll-off characteristic of this ideal probe must also be controlled to minimize pulse response aberrations. A real probe amplitude response, although designed to be flat over a broad frequency range, will exhibit some gain variation, particularly at frequencies above 1 GHz. It should be noted that the gain accuracy specification for the P7350 probe is specified as 2% at DC. The probe gain and accuracy is specified at DC primarily for convenience in measurement. Although the P7350 gain is relatively flat from DC out to about 1 GHz, as shown in Figure 8, the probe gain accuracy deviates noticeably from the DC specification at frequencies above 1 GHz. At the specified bandwidth limit of 5 GHz for the P7350 probe, for example, the gain may be rolled off as much as 3 dB, which is a reduction in gain of about 30% from the DC voltage gain.

The DC voltage gain of the P7350 probe is specified to be 0.16, which represents a 6.25X attenuation of the input signal. This 6.25X probe attenuation results from the combination of the probe input attenuator and the fixed probe amplifier gain. A simplified diagram of the P7350 probe architecture is shown in Figure 9, which shows the probe input attenuator and buffer amplifier. In order to meet the

Figure 8. P7350 gain response with frequency (single-ended).

DC gain accuracy specification of 2%, the P7350 input attenuator is laser trimmed during manufacture with its buffer amplifier active. Because of the intelligent TekConnect interface between Tektronix probes and oscilloscopes, the DC gain of the probe is usually transparent to the user. The oscilloscope automatically scales its internal gain control to match the oscilloscope vertical scale factor with the specified probe gain. Information about the probe DC gain is stored in a non-volatile memory in the probe and is read by the oscilloscope when the probe is attached. It is also possible to optimize the accuracy of the system gain and offset of the probe and oscilloscope by exercising the Probe Cal process on Tektronix oscilloscopes. Probably the most important amplitude response specifications for the P7350 probe are its differential and common mode input range specifications. The differential mode input range represents the effective dynamic range of an input differential signal. To try to prevent inadvertent overdriving of the probe amplifier, many Tektronix oscilloscopes now show temporary annunciation markers at the dynamic range limit when the vertical scale or position is adjusted near the range limit. The differential mode input range of the P7350 probe is  $\pm 2.5$  V, which is communicated over the TekConnect interface to allow the oscilloscope to set its dynamic range markers correctly. The common mode input range represents the DC voltage range with respect to ground that can be applied to both of the probe input pins without limiting the probe response. Because of the high CMRR of the P7350 probe, a common mode

Primer

Figure 9. P7350 simplified block diagram.

DC signal within the +6.25 V and -5.0 V common mode input range will be reduced to a mV level DC offset voltage. It should be noted that the bandwidth and rise time specifications for the P7350 probe are measured with small input signals. The P7350 probe, however, has been designed to give usable speed for large signals as well. The common mode input range is not the same as the maximum non-destructive input range, which represents the input damage voltage limit of the probe. When an input signal is measured within the  $\pm 2.5$  V differential signal range of the P7350 and also within its +6.25 V to -5.0 V common mode range, the signal should be processed with excellent linearity and gain accuracy by the probe buffer amplifier. The differential mode input range of the P7350 probe can be expanded an additional  $\pm 1.25$  V by applying a differential signal offset to the probe. This differential offset control is applied to the probe from the connected oscilloscope over the TekConnect interface. As shown in the simplified block diagram in Figure 9, the DC offset signal from the oscilloscope is buffered by a singleended amplifier in the P7350 Compensation Box control board and passed to the offset input of the probe head amplifier. The probe head amplifier then converts the single-ended offset signal to a complementary differential offset signal that drives the ends of the input attenuator. The differential offset signal effectively cancels out differential DC voltages applied to the P7350 input pins. The differential offset control is perhaps most useful for single-ended

Figure 10. P7350 CMRR response.

measurements made with the P7350 differential probe. A singleended measurement is made with a differential probe by grounding the probe –Input pin. If a single-ended DC voltage is present at the probe +Input pin, it is effectively converted to a DC differential mode voltage:

$$V_{\text{DIFF}} = V_{+} - V_{-} = V_{\text{DC}} - 0 = V_{\text{DC}}$$

This DC differential mode voltage can be nulled out using the differential offset control, if it is within the  $\pm 1.25$  V differential offset range. By nulling out this DC differential mode voltage, the P7350 dynamic range window is effectively expanded, although the  $\pm 2.5$  V differential signal range limit still applies within the expanded dynamic range window.

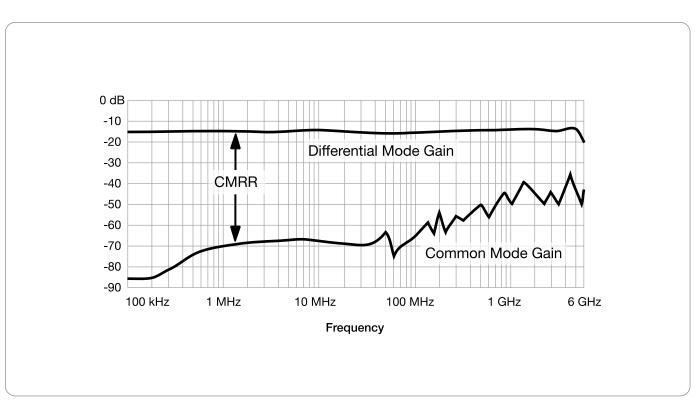

The common mode rejection ratio (CMRR) specification for the P7350 probe is specified at several frequencies from DC to 1 GHz. CMRR is defined as the ratio of differential mode gain to common mode gain. CMRR is effectively a measure of how well matched the two differential signal paths of the probe input have been designed and manufactured. Path mismatch, particularly at higher frequencies, can cause some of the differential mode signal to be converted to a common mode signal, which reduces CMRR. Because of increasing parasitic effects with increasing frequency, CMRR drops off with frequency as shown in Figure 10. On the log-scale display of differential mode and common mode gain over frequency in Figure 10, CMRR can be calculated by simply subtracting DM gain in dB from CM gain in dB at any frequency:

#### $CMRR = A_{DM}(dB) - A_{CM}(dB)$

The CMRR performance of the P7350 probe is measured with a network analyzer, which has a very controlled impedance environment. The CMRR that is observed in an actual differential measurement application will be affected by signal source and load impedance mismatch as well as differential signal skew and other routing variations.

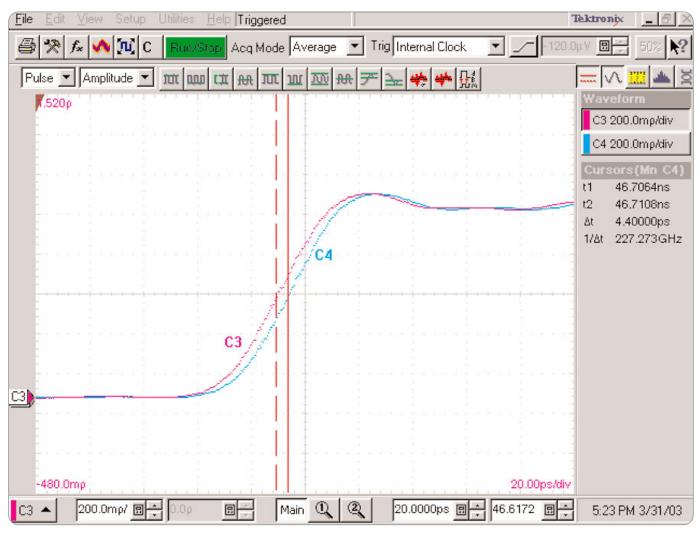

#### **P7350 Timing Response**

The two key timing response parameters for an oscilloscope probe are bandwidth and rise time. Bandwidth is a frequency domain representation of a probe's timing performance and is defined as the frequency at which the probe DC gain has fallen by 3 dB. Rise time is a time domain representation of a probe's timing performance and, in general, is defined as the time interval between the 10% and 90% crossing points on a step (pulse) waveform. Although for a known signal response characteristic there is a fixed relationship between bandwidth and rise time, the response of high-speed probe amplifiers varies enough that the traditional bandwidth-rise time product of 0.35 for a Gaussian amplifier is not very accurate. Because an oscilloscope is fundamentally a time domain instrument, Tektronix guarantees probe rise time performance and specifies probe

Primer

bandwidth as typical. Although probe bandwidth may be a typical specification, it is nevertheless a measured rather than a calculated parameter for Tektronix probes and has well defined manufacturing quality limits.

The bandwidth of the P7350 differential probe is specified as DC to  $\geq$ 5 GHz. Bandwidth is specified as a typical, probe-only specification. It is measured using a doubly terminated probe test fixture, which results in an effective 25  $\Omega$  source impedance. For ease in manufacturing, bandwidth is currently made as a single-ended measurement using a network analyzer with one probe pin grounded. Differential mode bandwidth performance has been verified however using mixed mode S-parameter methods. Although the measurement system bandwidth when using a P7350 depends on the bandwidth of the host oscilloscope, the traditional root-mean-square calculation combining the oscilloscope bandwidth and the probe-only bandwidth should not be assumed valid. The intelligent TekConnect interface allows TekConnect oscilloscopes to identify the attached probe type and take control measures to optimize the system bandwidth. The P7350 probe when used with the 6 GHz TDS6604 oscilloscope, for example, has a system bandwidth of 5 GHz, limited largely by the probe response. Similarly, the P7350 probe when used with the 4 GHz TDS7404 oscilloscope has a system bandwidth of 4 GHz, limited in this case by the oscilloscope bandwidth. In both of these cases, the system bandwidth is better than expected, based on a root-mean-square calculation combining the probe-only bandwidth and oscilloscope bandwidth.

The 10–90% rise time of the P7350 differential probe is specified as  $\leq$ 100 ps. Rise time is specified as a guaranteed, probe-only specification. It is measured using the same doubly terminated probe test fixture used for bandwidth measurement. Because the system rise time of the applied pulse source and sampling oscilloscope used to measure probe rise time is only about 30 ps, the probe rise time must be extracted from the measurement using a root-mean-square calculation:

## rise time<sub>probe</sub> = $\sqrt{(rise time_{system&probe}^2 - rise time_{system}^2)}$

Since many serial data standards now specify 20–80% rise time measurements, the P7350 has specified a typical 20–80% probe rise time of  $\leq$ 65 ps. This value, which has been verified thoroughly with probe testing, also agrees with the general rule of thumb relationship between 10–90% rise times and 20–80% rise times:

#### **Differential Probe Attachment Issues**